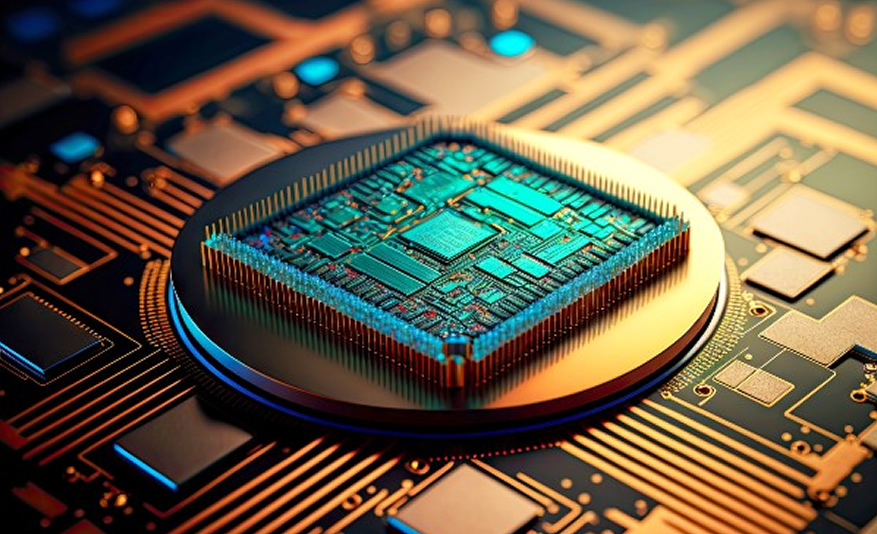

Hybrid bonding, also known as direct-bond interconnect, is poised to transform a semiconductor industry wrestling with Moore’s Law slowing as market demands for ubiquitous access to more data rise. While the industry turned to advanced packaging solutions in this More-than-Moore Era, there is an emerging consensus that the limits of conventional packaging technology may well have been reached. This stark realization has put a growing community of scientists and engineers on a quest to identify and deploy technologies that allow for a higher density of interconnects than traditional copper microbumps.

Hybrid bonding meets this requirement by reducing the interconnect size, enabling more efficient and faster signal transmission. The technology has roots in research from the late 2000s to early 2010s. Significant advancements have taken place over the past few years, as companies and research institutions, largely led by Adeia, develop and refine techniques to address the growing demand for higher performance, greater interconnect density and improved thermal management in semiconductor devices.

Hybrid-bonding attributes

Among the many attributes driving interest in—and adoption of—hybrid bonding is its ability to allow chips from different nodes, functions and manufacturers to be assembled heterogeneously while behaving as if monolithically built. The concept of designing chiplets—small portions of functionality in silicon—and connecting them with standard interfaces has created a revolution in the industry.

The combination of hybrid-bond interconnect with chiplet architectures promises to ease the cost of product generation evolution by:

Reducing dependence on product roadmaps for transistor node scaling, which is slow and exceedingly expensive

Creating access to affordable standardized chiplets that are combined at the packaging level, which reduces costs while bringing down barriers to entry for system-on-chip (SoC) innovation and manufacturing operations

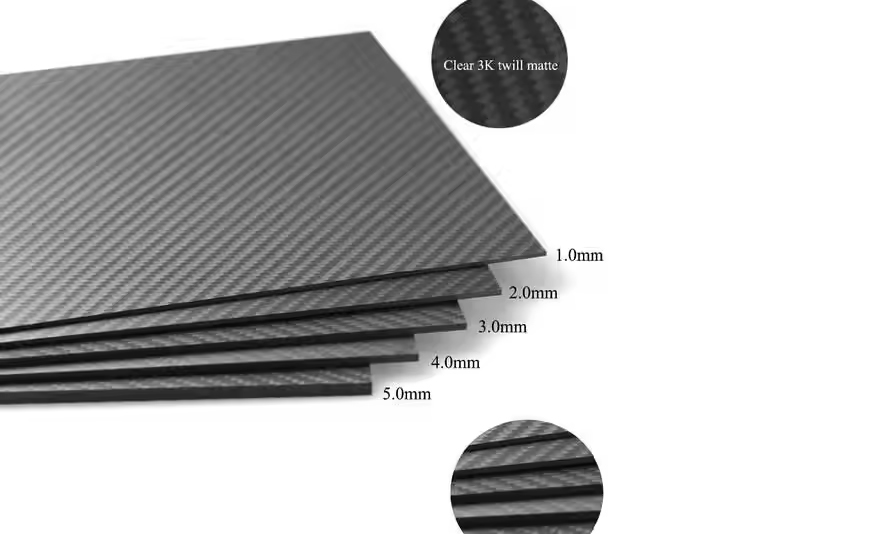

Hybrid bonding can achieve a minimum pitch as small as 0.4 µ, significantly smaller than the 35-µ minimum pitch of traditional microbumps. This efficient electrical conduit offers a higher density of input/output (I/O) connections with lower inductance, capacitance and resistance, resulting in faster and lower-power signal transmission. It is formed as part of a standard integrated-circuit wafer process, thereby reducing the number of additional steps to fabricate the interconnect. By contrast, a solder microbump requires multiple process steps outside of the foundry.

The shorting and reliability concerns associated with shrinking microbumps and solder reflow assembly are eliminated with hybrid bonding. Moreover, hybrid interconnect bonding occurs at room temperature, unlike microbumps, which require heating to improve alignment accuracy and throughput assembly processes.

These attributes are why hybrid bonding is considered a transformative technology in the advanced packaging world and is being adopted in areas of the semiconductor industry in which the advantages of the technology are instrumental in addressing product performance differentiation.

Hybrid bonding in action

One of the main applications for hybrid bonding is in image sensor manufacturing. Sony led the way, capturing significant market share by transitioning early to this manufacturing technology, which enabled the company to realize stacked image sensors delivering differentiated product features. Now, more than 90% of the industry is using direct bonding and hybrid bonding in their product.

More recently, a few NAND manufacturers (YMTC, Kioxia and WD) have adopted hybrid bonding by rolling out new architectures with enhanced performance. The remaining manufacturers are reporting plans to adopt hybrid bonding within a few years, indicating its imminent use in memory applications.

The technology is also being utilized in the radio-frequency space, where low I/O density and high speed are required. Furthermore, many dynamic random-access memory and high-performance compute module manufacturers are preparing their production lines for the introduction of hybrid-bond interconnects within their products. AMD, a fervent promoter of chiplet architecture, has released several product generations of hybrid-bonded SoCs since 2022.

Advantages of hybrid bonding

Higher I/O density: Hybrid bonding allows for 10,000× higher interconnect density per area compared with microbump technology, significantly increasing connectivity between chips and enabling faster signal transmission with lower power consumption.

Lower inductance, capacitance and resistance: The reduced size of hybrid-bond interconnects leads to lower inductance, capacitance and resistance. This results in faster signal transmission, lower power consumption and improved overall performance.

Scalability: Because hybrid bonding can scale to submicron pitches, it allows for finer and more precise interconnects. Research has demonstrated a 0.4-µ pitch, with even smaller pitches possible in the future.

Simplified manufacturing process: Switching to a hybrid-bond interconnect in high-bandwidth memory requires fewer steps in the process compared with microbump methods, leading to cost savings and increased efficiency. The process involves about 11 fewer steps, resulting in more streamlined and efficient production.

Flexibility for system architects: Hybrid bonding provides system architects with greater creative freedom in designing chips and systems, facilitating the integration of heterogeneous components and enabling the construction of systems on a chip. This flexibility allows for customized and optimized systems based on specific requirements.

Thermal performance benefits

The semiconductor industry has focused on increasing density and stacking dies vertically, which has led to thermal challenges. Hybrid-bond interconnect interfaces improve thermal performance by reducing the temperature difference between the dies within a chip stack compared with traditional packaging methods. This allows for better efficiency and speed in accessing memory and other functionalities, enabling the stacking of multiple dies without compromising performance.

Hybrid-bonding technology, in short, is set to become a game-changer in the semiconductor industry, promising higher performance, lower power consumption and enhanced efficiency in chip manufacturing and design.