Powerchip Semiconductor Manufacturing Corp. (PSMC) has partnered with AP Memory to launch an innovative 3D AI Foundry strategy, designed to address the demanding high-performance, low-power needs of artificial intelligence (AI) systems. Through advanced 3D multi-layer stacking and interposer technologies, PSMC aims to overcome the memory bandwidth and power constraints of current 2.5D architectures, establishing itself as a valuable partner for AMD and multiple outsourced semiconductor assembly and test (OSAT) companies in next-generation AI computing advancements

Building a Strong Foundation with India Tata Group

Following the release of PSMC’s 3Q financial results, Chairman Frank Huang introduced the 3D AI Foundry as one of the company’s four main business pillars: logic foundry, memory foundry, 3D AI Foundry, and FAB IP. As part of this strategic expansion, PSMC has partnered with Tata Electronics, India’s largest conglomerate, which will bring in phased revenue surpassing $6.25 billion over the next few years. Tata Electronics, with 50,000 employees, is the country’s largest electronics producer, contributing to Apple’s mobile production and aiming to establish a complete electronics supply chain.

On September 25, Chairman Huang and PSMC CEO Hsien-Kuo Chu visited India to meet Prime Minister Narendra Modi and senior officials. This collaboration, fully in line with the FAB IP model, PSMC will support Tata in fab construction, employee training, and technology transfer, earning phased service and licensing fees over the coming years.

Pioneering 3D AI Technology with Multi-Layer Stacking

PSMC’s early $60 million investment in 3D technology is expected to yield mass production capabilities at its new Tongluo facility within the next few months, with volume production projected by late next year to meet surging AI demand. A planned investment of $3 billion aims to boost production capacity significantly, positioning PSMC at the forefront of advanced 3D AI solutions.

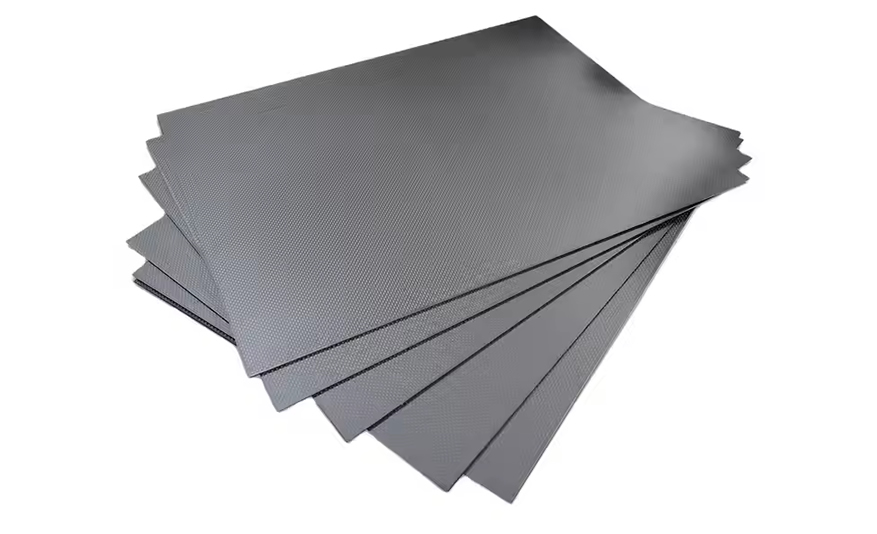

PSMC’s 3D multi-layer stacking technology addresses critical challenges in AI systems, particularly for high-bandwidth memory (HBM), where power efficiency and heat management are vital. AP Memory Chairman Chen Wen-Liang highlighted that transitioning from 2D and 2.5D to 3D stacking reduces interconnect distances from millimeters to micrometers, enhancing bandwidth tenfold and cutting power consumption to one-tenth of a picojoule per bit. Stacking multi-layer DRAM on a single logic chip further increases capacity to support AI workloads efficiently.

From an application standpoint, Chen expects that cloud-based AI applications utilizing HBM3 and HBM4 will gradually shift to On-Device AI and other edge applications, responding to a growing need for reduced power consumption. While On-Device AI technology is still maturing, the power and bandwidth benefits of 3D architecture are anticipated to drive this market rapid growth.

Future of AI Computing with 3D Chips

“3D AI chips represent the computing architecture of the future,” remarked PSMC’s Chief Technology Officer S.Z. Chang. He emphasized the need for advanced packaging to enhance performance and reduce power consumption in computational processes. Transitioning from 2.5D to a 3D stacked integrated architecture, where memory is directly stacked on computing units, enables higher bandwidth and lower power consumption.

For the 3D AI Foundry, PSMC offers a range of 3D wafer-on-wafer (WoW) stacking technologies, including DRAM multi-wafer, logic and DRAM, and logic and logic/CIS stacking. Chang highlighted that the company’s 3D wafer-on-wafer (WoW) stacking technologies, including four-layer stacking with through-silicon via (TSV) and Hybrid Bonding technologies, are designed to meet the dense interconnect requirements of analytical AI, generative AI, and high-performance computing (HPC) applications.

PSMC’s breakthrough four-layer 3D memory stacking technology is process-agnostic, allows support for both mature and cutting-edge processes, from 28nm down to 3nm, providing flexibility to cater to various foundry needs. In partnership with ITRI, PSMC’s 3D AI chips integrate SoC and DRAM interconnects, achieving bandwidth over ten times higher than traditional 2.5D HBM interconnects while reducing power consumption by one-seventh.

By next year, PSMC plans to double or even triple its capacity for high-capacity integrated passive device (IPD) interposers, which have successfully passed OSAT certification. As PSMC continues to enhance its 3D AI capabilities, its advancements in power efficiency and data transfer will likely define the future of AI computing, enabling applications across a range of performance-critical sectors.